半导体行业观察

最有深度的半导体新媒体,实时、专业、原创、深度,60万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。

共发布文章50篇

铁电半导体,扮演重要角色

在研究人员看来,铁电半导体是将主流计算与下一代架构连接起来的竞争者,现在密歇根大学的一个团队已经将它们制造得只有 5 纳米厚——大约只有 50 个原子的跨度。

2023-02-07 15:15:08

Chiplet,还有不少难关要过

近日,Chiplet峰会在美国隆重举行,从会议的讨论可以得到的一个主题是:摩尔定律已死,我们只剩下封装了。

2023-02-07 15:12:17

GaN,迎来新突破!

如今采用了宽禁带材料的功率半导体已经开始实用化。

2023-02-07 15:04:37

德勤对半导体的预测,人才会成为大问题

半导体人才在 2022年供不应求——预计到 2023 年,部分行业的短缺情况将更加严重,并成为未来十年的挑战。

2023-02-06 18:42:53

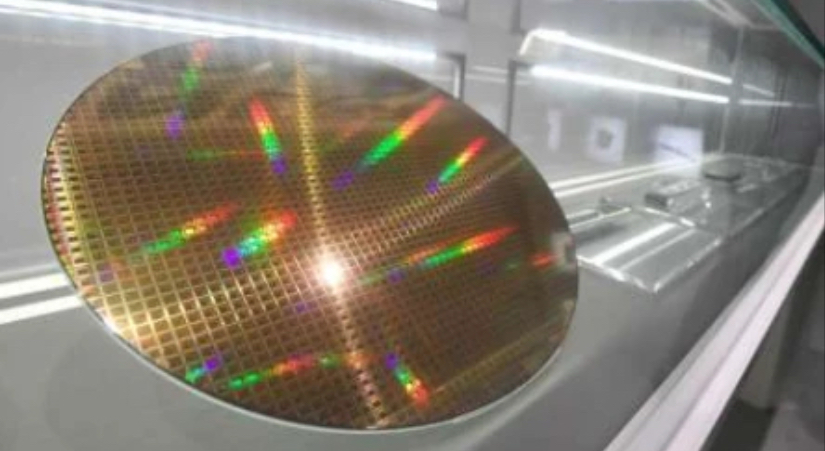

光罩,国内奋起直追!

和晶圆厂(wafer fab)相比,光罩厂的规模和产能都要小很多,但是作为光刻工艺中不可缺少的材料,光罩的成本也占到光刻成本的将近一半,其地位自然是相当重要的!光罩在FPD,集成电路的前后道光刻中都是必须的材料。

2023-02-06 18:05:40

芯片设计行业的新趋势

芯片设计随着时间推移正在变得越来越复杂是业界人士的共识,但是究竟“复杂”体现在哪些方面,并且随着复杂度提升,还有哪些没有解决的问题,这就需要深入的考察和研究。

2023-02-02 14:38:11

韩国芯片,创纪录的大溃败

由于芯片销售和芯片价格暴跌,韩国 1 月份报告了有史以来最大的贸易逆差。

2023-02-02 14:35:18

车厂争抱SiC巨头大腿

汽车所引爆的SiC需求正在急剧增长,根据投资银行Canaccord Genuity预计,碳化硅晶圆产能将从2021年的12.5万片6英寸晶圆增加到2030年的超过400万片6英寸当量晶圆,来满足电动汽车市场的需求

2023-02-02 14:31:59

手机芯片这个功能,有望改变市场格局!

曾经,我们只能在PC或主机端体验到画面细腻精致和流畅的3A游戏,而现在,手机厂商大力投入自研芯片,将光线追踪等技术做到手机里,移动GPU处理性能也越来越强劲。

2023-01-31 17:02:27

苹果披露自研PC芯片的原因

来源:内容由半导体行业观察(ID:icbank)编译自雅虎财经,谢谢。

2023-01-31 17:00:41

EUV光刻的两大挑战者,谁扛大旗?

自仙童半导体公司的罗伯特诺伊斯在1960年发明单片集成电路以来,光刻技术一直是主要的光刻技术。

2023-01-31 16:57:37

2023年,全球芯片产业不容乐观

由智能手机、个人电脑和家用电器组成的消费电子市场疲软是芯片行业进入下行周期的最重要因素。

2023-01-31 16:55:03

Arm的崛起故事!

尽管走了一条意想不到的道路,但公司创始人的成功超出了他们最疯狂的梦想。

2023-01-29 14:06:02

半导体衰退,比我们想象严重得多

我们的分析表明,经济衰退远比业内公司和华尔街预期的要严重。

2023-01-29 13:57:59

将光集成到硅芯片,有新思路

传统 IT 一直依赖摩尔定律的持续红利。对于人工智能 (AI) 来说,这可能是一场灾难,它正处于大规模扩张的边缘…

2023-01-29 11:49:43

美国掀起建晶圆厂热潮,但低估了难度!

到 2030 年,正在进行、已宣布或正在考虑的美国半导体项目的总价值将达到 2230 亿美元至 2600 亿美元以上。

2023-01-29 11:27:40

芯片工程师,百万年薪算多吗?

拿到百万年薪的芯片工程师主要有三类

2023-01-29 11:24:26

CXL的崛起

CXL 在大型数据中心内越来越受欢迎,作为提高不同计算元素(如内存和加速器)利用率的一种方式,同时最大限度地减少对额外服务器机架的需求。

2023-01-29 10:30:21

背面供电,可以怎么玩?

本文中,我们采用BPR技术对PDN进行了全面的设计研究,考虑了不同可能的功率传输配置。通过64位高效CPU(如Cortex-A53)在低于5nm节点的物理设计实现,我们评估了系统级影响,对比了FS、FSBPR和BSBPR的功率、性能和IR压降表现情况。

2023-01-29 10:27:50

CUDA正在被赶下神坛?

随着 PyTorch 2.0 和 OpenAI 的 Triton 的到来,英伟达在该领域主要依靠其软件护城河的主导地位正在被打破。

2023-01-17 15:39:28

EUV光刻,最终胜出!

上世纪90年代后半期,大家都在寻找取代193nm光刻光源的技术,为了把193nm的光波“磨”细,大半个半导体业界都参与了进来。

2023-01-17 15:32:58

芯片流片为什么这么贵?

流片是一件非常烧钱的事,多几次流片失败,可能就会把公司搞垮。2019年就曾传出小米旗下松果电子的澎拜S2系列芯片连续5次流片失败,设计团队重组的惨痛案例。

2023-01-17 15:27:56

被一颗芯片拿捏的中国车厂

半年内发生的短短三个事情看来,中国智能汽车厂商似乎都已经被高通抓住了“命脉”。就和过去十年的国产智能手机一样。

2023-01-17 15:21:56

TI中国MCU研发团队解散了?我和知情人聊了聊!

不要盲目迷信外国厂商,因为他们也会在部分芯片上犯一些我们认为他们绝对不会犯的错误。

2023-01-17 15:17:14

芯片公司招人难,留人更难

虽然芯片行业人才供不应求,但依然缺少成熟的人才培养机制。

2023-01-17 10:09:56

排队上市的珠海芯片公司

近来,随着中科蓝讯的上市,少被提及的珠海芯片产业又一次吸引了大家的目光。

2023-01-16 19:16:08

一文看懂WiFi 7

如今,由一系列 IEEE 802.11 标准定义的 Wi-Fi 是最流行的数据传输无线技术。

2023-01-16 19:09:10

芯片出口激增,台湾仍是半导体龙头

台湾集成电路芯片出口在 2022 年连续第七年增长,进一步巩固了台湾经济在全球半导体行业的领导地位。

2023-01-16 19:04:22

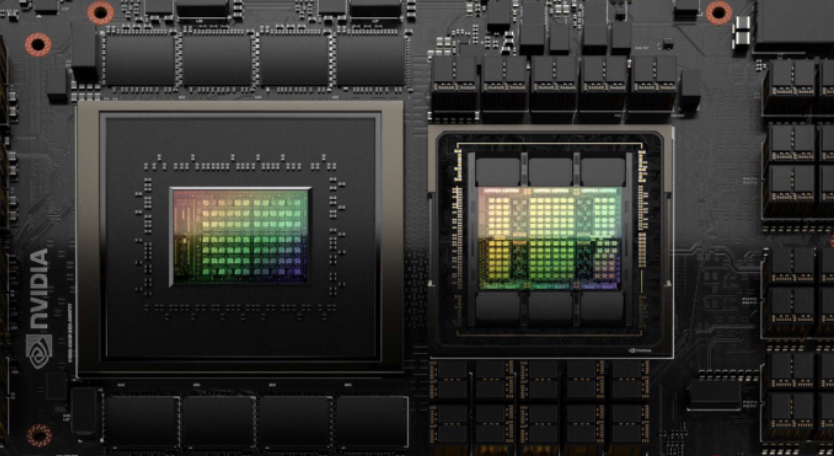

英伟达,落后了?

虽然摩尔定律已经逐渐走到尽头,但我们却来到了一个更加看点十足的时代。

2023-01-16 18:59:35

苹果又一颗自研芯片曝光,博通是受害者

苹果是博通最大的客户,在上一财年为这家芯片制造商贡献了约 20% 的收入,接近 70 亿美元,而这个部件就是WiFi和蓝牙芯片。

2023-01-12 15:56:53

台积电正在研究的新型存储技术

但是随着半导体制造技术持续朝更小的技术节点迈进,传统的DRAM和NAND、Flash面临越来越严峻的微缩挑战。

2023-01-12 14:39:02

MCU的十年往事

MCU从1970到1980年的辉煌十年

2023-01-12 11:47:30

国产射频,格局初定

2023年是国产射频前端芯片格局初定的一年,各个细分赛道都将迎来上市公司。

2023-01-12 11:39:33

美国“抢滩”SiC市场

如今凭借更宽的带隙、抗高压高温、能够在大功率范围内进行工作等诸多优点,SiC成为电动汽车崛起的关键,SiC也真的要成为芯片行业的“钻石”了。

2022-11-07 09:04:35

疯狂的IDM

在过去那段极其严重的缺芯潮器件,相较于只能依赖代工厂、需要进行产能争夺的芯片设计企业,IDM厂商的优势及其明显,稳定的产能供应、较短的交货周期、更强的设计生产能力的适应性…

2022-10-21 09:40:42

三星痛失半导体老大背后

在过往,半导体龙头位置一直由三星和英特尔争霸,但现在他们双双落败,由做晶圆代工的台积电迅速补上。在这背后,其实藏着一场半导体产业的新变化——一个全新的半导体产业格局正在迅速重建。

2022-10-16 18:49:30

模拟芯片,也撑不住了?

半导体产业的抗跌“独苗”好像要撑不住了。

2022-10-13 09:41:32

关于芯片,汽车厂商策略要变了!

展望未来,可以预测,特别是成熟技术节点的半导体,短缺将持续到2025年以后

2022-10-10 20:00:41

汽车芯片高增长背后的“隐忧”

随着汽车电动化、网联化、智能化、共享化“新四化”的趋势不断加速,半导体在汽车中的占比越来越高。据悉,一辆传统汽车一般需要用到500-600颗的芯片,而一辆新能源汽车所需的芯片更多,达到1000颗以上。到2030年,汽车50%的成本将与芯片相关,而汽车制造商80%的创新将由芯片驱动。

2022-09-27 09:27:57

小心,半导体下行周期来袭

近日,多家研究机构数据表明,全球半导体市场增速正在放缓,半导体市场正在进入一个从热向冷的周期性转变。

2022-09-19 13:46:39

苹果A系列芯片,辉煌不再?

从手机A系列芯片到手表S系列/W系列芯片、耳机芯片H系列以及电脑M系列芯片,苹果给广大用户创造了一个个惊喜。作为该公司自研定制芯片最成功之一的手机A系列芯片,伴随着A16 Bionic芯片的发布,目下市场上开始出现了一些不同的声音,“挤牙膏”、“提升不大”等等。苹果A系列芯片真的辉煌不再了吗?

2022-09-16 19:44:57

存储大厂又一次豪赌

过去两年,缺芯潮和涨价潮此起彼伏,席卷全球。进入2022年,曾经火热的终端市场开始逐渐冷却。

2022-09-15 21:06:57

MEMS,中国半导体的另一个突破口?

MEMS行业作为基于集成电路技术演化而来的新兴子行业,这几年发展迅速,如今,MEMS传感器和执行器已成为日常生活的一部分,2021年对于MEMS公司来说是不平凡的一年,这一年大多数MEMS厂商迎来了可观的增长。

2022-09-13 09:40:11

英特尔,三年后重返巅峰?

半导体行业观察 最有深度的半导体新媒体,实时、专业、原创、深度,60万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。

2022-09-09 17:19:45

淘汰赛开打,国产芯片公司的五种“死法”

以终为始,方得始终。从开始就要考虑到最终的结果,中国市场最终不需要那么多芯片公司,大浪淘沙,胜者为王。

2022-09-06 16:24:44

国产算力赛道战火升级,瀚博锋芒已露

未来的像素世界需要强大的算力,但如果像素世界只能看而不能产生,那不是我们的完整拼图,我们的目标就是把算力相关技术完美结合在一起!

2022-09-05 13:39:53

美国大举兴建晶圆厂,十年投资2000亿美元

半导体行业观察 最有深度的半导体新媒体,实时、专业、原创、深度,60万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。

2022-08-31 09:49:47

半导体设备供应商TOP 20榜单背后

半导体行业观察 最有深度的半导体新媒体,实时、专业、原创、深度,60万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。

2022-08-30 09:43:41

从Hotchips看芯片行业走势

Hotchips是全球最具有影响力的芯片会议之一,其主要针对芯片工业界展示最新的研发成果,以及披露最新产品中的重要技术。上周,第34届Hotchips刚刚落下帷幕,本文将本届Hotchips中表现出来的业界动向做一个分析。随着人工智能等高性能计算应用的持续火热,这些方向也成为了半导体芯片行业发展最重要的驱动力之一。本届Hotchips的亮点无疑是支持这些应用方向的芯片,尤其是应用于边缘和数据中心的这类高性能计算赋能芯片。在本届Hotchips共两天七个主题议程中,约有一半的相关论文和这些高性能计算有关,涵盖了GPGPU、机器学习加速、ADAS和高性能网络开关等领域,而这些相关论文都来自Nvidia、AMD、Intel、Tesla等业界最顶尖的芯片公司,论文内容则是关于公司最新芯片的关键技术。这些赋能云端高性能计算的芯片有一个共同的特点,就是规模越做越大,而本届Hotchips中我们也可以看到芯片设计行业正在使用全新的工具来确保芯片规模的继续上升,而这些工具就是芯片粒/高级封装以及芯片-软件协同设计。如果说基于IP复用的SoC理念创造了上一代大规模集成芯片的蓬勃发展的话,那么芯片粒和软件协同设计将会成为芯片突破集成度瓶颈并进一步提升芯片功能和晶体管规模的下一代支柱。芯片粒是未来高性能芯片的支柱随着高性能计算对于芯片性能(包括算力、互联和内存接口)的需求持续上升,整个芯片系统的晶体管规模和设计复杂度也在相应提升。这样的性能需求上升是指数级的:以Nvidia的GPU算力为例,一般的规律是每一代(两年)GPU的性能相对于上一代提升两到三倍。为了应对指数级上升的性能需求,芯片系统必须要从两个方面实现不断提升,其一是单芯片的性能,其二是可扩展性。单芯片的性能提升约等于在芯片中加入更多的晶体管,其主要挑战在于如何提升良率和降低成本,因为芯片的良率随着晶体管数量提升(即芯片面积上升)而快速下降,单纯堆积晶体管的做法会导致良率低到无法接受。除此之外,还需要确保芯片系统设计是可扩展的,即可以把多个单元芯片协同工作以进一步提升性能。可协同性的主要挑战在于IO带宽,如果IO成为瓶颈的话,那么多个单元芯片协同工作的性能并不会比单元芯片强很多。为了解决良率和可扩展性的问题,芯片粒加高级封装技术就成为了目前芯片厂商普遍的答案。在这样的方案中,首先不再追求每个单元芯片的集成度,而是把单元芯片做成面积较小的芯片粒,这样芯片粒的良率会远远高于大芯片。同时,将多个芯片粒用高级封装的技术集成到一起来实现大规模芯片系统,由于高级封装技术同时提供了大带宽的高性能互联,这样就就解决了可扩展性问题。在本届Hotchips上,我们可以看到芯片粒加高级封装已经成为了高性能计算的主流解决方案。Intel的Ponte Vecchio是本届Hotchips的一大亮点:Ponte Vecchio是Intel的下一代GPU架构,其设计中使用了大规模芯片粒和高级封装技术,而在本次Hotchips上Intel公布了Ponte Vecchio的最新架构细节和相关数据。在Ponte Vecchio中,会有多个Xe 核心使用高级封装(EMIB)的方式组成compute tile,而L2 Cache则有相应的一个芯片粒(称为Cambo cache tile),并且和compute tile集成到一起。而除此之外,还有HMB和用于芯片间互联的Xe Link芯片粒,这些芯片粒组成了整个Ponte Vecchio系统。由于使用芯片粒的方式,我们看到Intel可以在良率可控的情况下加入大量的Xe核和海量缓存(cache):整个Ponte Vecchio包括了128个Xe核,64MB的register file,64MB的L1 cache和408MB的L2 cache。整个Ponte Vecchio系统可以实现839 TFLOPS的峰值浮点数算力以及1678 TOPS的峰值整数算力,在实现如此高算力的超大规模芯片系统中,芯片粒和高级封装技术可谓是居功至伟。在Intel的Ponte Vecchio之外,Tesla也公布了其用于人工智能模型训练的Dojo芯片。在Dojo芯片系统中,其基本的计算chiplet是D1,每个D1包括了362TFlops算力和440MB SRAM,同时每个Dojo则包含了25个这样的D1芯片粒以及40个专用的IO芯片粒,使用TSMC的system-on-wafer技术集成到一起,从而实现超大算力支持。在Intel和Tesla之外,AMD在本届Hotchips上也带来了其MI200系列高算力GPU加速芯片,这也是全球第一个使用芯片粒技术的GPU。AMD将两块芯片粒封装在一起,同时使用400GB/s的高带宽封装内互联确保不同的芯片粒之间能高效互联,每个芯片系统包含了580亿个晶体管,使用TSMC 6nm制造。MI200是AMD在GPGPU领域的重要布局,我们从中看到芯片粒也起了至关重要的作用,而在其下一代MI300 GPGPU目前公布的信息来看,AMD将会进一步加强芯片粒和高级封装技术的作用,从而实现更大规模和更高性能的芯片系统。芯片和软件协同设计将成为主流在芯片粒之外,另一个值得我们关注的动向是芯片和软件协同设计。如前所述,芯片系统的规模正在越来越大,模块越来越多,功能越来越复杂,如果没有一个好的软件系统和生态的话,具体的应用很难充分利用芯片提供的性能,从而看到的就是实际应用中的实际性能和芯片的峰值性能相差甚远。更进一步,随着人工智能这类算法驱动类应用的火热,如何结合算法来做芯片的优化和设计也是进一步提升芯片性能的重要方法之一。而我们在本届Hotchips上也确实看到了软件和算法相关优化成为了厂商在演讲内容中的重点。Intel在本届Hotchips上的Ponte Vecchio演讲中,一个重点就是其OneAPI软件接口以及DPC++工具。OneAPI使用一个API来支持不同的底层硬件,从而理想的情况下无需修改应用的软件代码,只需要在OneAPI中直接指定相应的后端执行硬件就可以。OneAPI计划会支持至少Intel的CPU和GPU,可望大大减少应用所需要的软件工作。另一方面,DPC++则是Intel对于目前CUDA生态的回应,使用DPC++可以将已有的为CUDA编写的程序直接移植到Intel的GPU上,这样就大大增加了Intel生态的吸引力。软件在Tesla的Dojo芯片中也起到了至关重要的作用。如前所述,Dojo的设计牵涉到大量的compute tile,如何在不同的compute tile之间分配任务就成了决定整体系统性能的关键;除此之外,如何在不同的Dojo芯片之间分配任务也决定了整体系统的可扩展性。在Tesla的解决方案中,编译器软件将会确保将模型并行化处理并且加载到不同的compute tile中,同时尽量保证模型需要的数据都能装入片上SRAM中以保证性能降低对外部DRAM的依赖。除了编译器之外,Tesla在软件-芯片协同设计中另一个值得一提的是使用了独特的数值表示方式,在常见的FP16和BFP16之外还支持自研的CFP8和CFP16格式的数值表示方式并且在芯片中做了相应支持。根据Tesla公布的材料使用CFP8和CFP16可以获得更好的模型训练效果,而这也是软件-芯片协同设计的很好例子。在Intel和Tesla之外,在本届Hotchips上和AI相关的演讲几乎都会涉及软件-芯片协同设计,其中包括了业界巨头如Nvidia(Hopper GPU中使用了FP8和Transformer Engine),以及新锐初创公司如Untether AI(公布了UAI FP8数制和imAIgine SDK)和壁仞(TF32+数制和BIRENSUPA软件平台)。我们认为,软件-芯片协同设计正在成为芯片行业进一步推动芯片规模更上一个台阶背后的重要支柱之一,只有在有了强而有力的软件支持,以及对于算法的深入理解后,芯片规模进一步提升才会有相应的回报。

2022-08-29 17:54:30

成就台积电霸主地位的六个人

半导体行业观察 最有深度的半导体新媒体,实时、专业、原创、深度,60万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。

2022-08-26 09:55:25